2008/07/31

I2C Slave VHDL

며칠전에 만든 I2C Slave VHDL.

잡다구리한 일로 바빠서 멀티 커넥션은 아직 테스트를 못했다.

조만간 멀티로 회로를 연결해볼 생각인데 시간이 날려나 몰러...

이거 만들면서 한가지 알게된건

INOUT 포트를 사용할 때는 output enable 시그널로 IN과 OUT을 명확히 분리해줘야 한다는거...

이거 몰라서 엄하게 풀업 저항만 열나게 바꾸는 삽질을 이틀동안 했었다.

여기에 INOUT 포트 구현 예제가 있다.

어찌나 친절한지...

또 한가지 알게된 꼼수로

SCL 클럭을 SCL_pos와 SCL_neg 두개의 시그널로 전달해서 상승/하강 엣지에 대한 프로세스를 구현했다. 아직 개초보라서 이런 꼼수가 아니면 ACK 출력을 만들수가 없었다.

SPI보다 속도도 훨씬 느린 주제에 구현하기는 드럽게 어렵다.

아 열받어...

2008/07/21

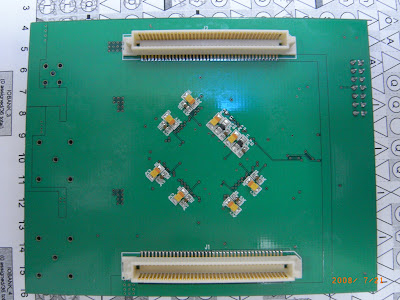

XC3S200-4VQ100C Module PCB

2008/07/17

EDID

Extended Display Identification Data는 호스트와 디바이스간의 정보 전달에 사용되는 128/256byte 데이터 덩어리다. EDID 1.3버전이 주로 쓰이는거 같고, 2.0버전은 256바이트라는구만.

자세한 내용은 여기에

"raw EDID"로 검색하면 다양한 소스를 구할 수 있다.

그럼 LTM190M2-L31(1440*900) 구동을 위한 EDID를 만들어 보자꾸나.

일단 EDID 데이터를 모아야지.

내가 쓰는 모니터

왼쪽은 싱크마스터 1280*1024, 오른쪽은 PCBANK 1920*1200

이놈들 EDID 값은

싱크마스터

0x 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F

------------------------------------------------

00 | 00 FF FF FF FF FF FF 00 4C 2D DD 01 36 31 36 4E

10 | 09 10 01 03 80 22 1B 78 2A AA A5 A6 54 54 99 26

20 | 14 50 54 BF EF 80 81 80 81 40 71 4F 01 01 01 01

30 | 01 01 01 01 01 01 30 2A 00 98 51 00 2A 40 30 70

40 | 13 00 52 0E 11 00 00 1E 00 00 00 FD 00 38 4B 1E

50 | 51 0E 00 0A 20 20 20 20 20 20 00 00 00 FC 00 53

60 | 79 6E 63 4D 61 73 74 65 72 0A 20 20 00 00 00 FF

70 | 00 48 56 47 4C 33 30 32 32 33 37 0A 20 20 00 CA

PCBANK

0x 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F

------------------------------------------------

00 | 00 FF FF FF FF FF FF 00 05 E4 01 00 01 00 00 00

10 | 01 0F 01 03 80 50 2D 78 2A EE 91 A3 54 4C 99 26

20 | 0F 50 54 A7 0B 00 A9 40 61 40 81 C0 81 81 45 41

30 | 31 41 71 41 D1 C1 58 1B 00 BA 50 00 1C 30 30 20

40 | 36 00 81 91 21 00 00 18 28 3C 80 B4 70 B0 16 40

50 | 30 20 36 00 81 91 21 00 00 1A 08 39 80 00 71 38

60 | 26 40 30 20 36 00 81 91 21 00 00 18 00 00 00 FF

70 | 00 0A 20 20 20 20 20 20 20 20 20 20 20 20 00 D4

머 이렇다.

해상도가 다르니까 이걸 그대로 쓸 순 없다.

아 어떡하지...

물론 총알같은 스피드로 검색

검색어는 "raw EDID 1440 900"

첫번째 검색결과에 1440*900 EDID 데이터가 나온다.

이런 훌륭한...

---------------------------------------------------------------------------

Monitor

Windows description......... CMO Monitor

Manufacturer description.... CMC 19AW

Manufacturer................ CMO

————————————————————————————

Plug and Play ID............ CMO2198

Serial number............... 0

EDID data source............ I2C bus (real-time)

————————————————————————————

Manufacture date............ 2007, ISO week 25

EDID revision............... 1.3

Display type and signal..... Analog 0.700,0.000 (0.7V p-p)

Sync input support.......... Separate

Screen size................. 410 x 260 mm (~20")

Power management............ Active off/sleep

Color characteristics

Display gamma............... 2.20

Red chromaticity............ Rx 0.642 - Ry 0.348

Green chromaticity.......... Gx 0.288 - Gy 0.601

Blue chromaticity........... Bx 0.143 - By 0.072

White point (default)....... Wx 0.313 - Wy 0.329

Timing characteristics

VESA GTF support............ Not supported

Horizontal scan range....... 30-82kHz

Vertical scan range......... 56-76Hz

Video bandwidth............. 140MHz

Extension blocks............ n/a

Timing recommendation #1.... 1440x900 at 60Hz

Modeline................ "1440x900" 106.500 1440 1520 1672 1904 900 903 909 934 -hsync +vsync

Standard timings supported

640 x 480 at 60Hz - IBM VGA

640 x 480 at 67Hz - Mac II

640 x 480 at 72Hz - VESA

640 x 480 at 75Hz - VESA

720 x 400 at 70Hz - IBM VGA

800 x 600 at 56Hz - VESA

800 x 600 at 60Hz - VESA

800 x 600 at 72Hz - VESA

800 x 600 at 75Hz - VESA

832 x 624 at 75Hz - Mac II

1024 x 768 at 60Hz - VESA

1024 x 768 at 70Hz - VESA

1024 x 768 at 75Hz - VESA

1152 x 864 at 75Hz - VESA

1280 x 960 at 60Hz - VESA

1280 x 1024 at 60Hz - VESA

1280 x 1024 at 75Hz - VESA

1440 x 900 at 60Hz - CMO

1440 x 1440 at 60Hz - VESA

Raw EDID base

00: 00 FF FF FF FF FF FF 00 0D AF 98 21 01 01 01 01

10: 19 11 01 03 68 29 1A 78 2E 4F A5 A4 59 49 99 24

20: 12 50 54 BF EF 00 81 80 81 40 71 4F 95 00 01 01

30: 01 01 01 01 01 01 9A 29 A0 D0 51 84 22 30 50 98

40: 36 00 98 FF 10 00 00 1C 00 00 00 FD 00 38 4C 1E

50: 52 0E 00 0A 20 20 20 20 20 20 00 00 00 FF 00 30

60: 0A 20 20 20 20 20 20 20 20 20 20 20 00 00 00 FC

70: 00 43 4D 43 20 31 39 41 57 0A 20 20 20 20 00 7C

---------------------------------------------------------------------------

CMO 1440*900 패널을 사용한 모니터에 들어가는거 같은데

이걸 써보자.

.

..

...

썅 안돼......

Peonix EDID Designer로 EDID 데이터를 확인해보니

Video Input Definition이 아날로그로 잡혀있다.

일단 Digital로 바꿔보자.

.

..

...

썅 또 안돼......

걍 VESA 홈페이지 가서 EDIDguideV1이란 문서를 읽어봤다.

다 좋은데 젤 끝에 Checksum은 머냐.....

This byte is programmed such that a one-byte checksum of the entire 128-byte EDID equals 00h. If the recorded checksum does not equal the calculated checksum then the checksum is invalid.

127바이트를 다 더한 다음 2의 보수면 된다는건가???

아 놔...바꿔본다.

.

..

...

된다......

해상도 외에 패널 스펙에 차이가 있을텐데...화질이 나쁘진 않어...

이건 EDID 데이터가 들어가는 I2C EEPROM.

ATmega128에서 I2C 인터페이스로 EDID 데이터를 writing 해준다.

흠 120Hz 구동 패널의 EDID도 함 디끼봐야것는걸...

물론 나중에

2008/07/16

PLL???

위에서 부터 순서대로 50MHz, 100MHz, 10MHz, 180MHz

50MHz 입력으로 100,10,180 MHz를 만들어 낸다.

워메 이런게 있었네...이제 오실레이터 구하러 안돌아댕겨도 되것네.

왜 이좋은걸 이제 알았을꼬.

사이클론3에 내장된 PLL을 구동하기위해 megafunction의 altpll을 사용했다.

megafunction 첨 사용해봤는데, IC 사면 딸려오는 C library 같다고나 할까...어째뜬 첨 써보는데

잘 돌아가니까 기분은 조아.

altpll_reconfig도 있는데

재컴파일 없이 외부 데이터 입력으로 PLL을 재구성 하도록 만들어 놓은거 같다.

문서를 읽어보면 자세히 알겠지만.....

난 소중하니까 필요하면 읽어보기로 한다.

그럼 이만.

2008/07/03

Test VHDL for Memory blocks In Cyclone III 세번째

몇일동안 ODCK, HSYNC, VSYNC, DE 신호를 측정하고 이리저리 주물러봤는데

결론은

DE 신호를 어찌 좀 주물러봐야 패널에 출력되는 영상을 64라인씩 밀어 올릴수 있다고 생각된다.

그러니까

이렇게 DE 신호를 입력 받아서 뒤로 밀어버리면 된다 이거지...

끝없는 삽질 끝에 드디어 완성했다.

test_VHDL

출력물도