일단 간단하게 가보자.

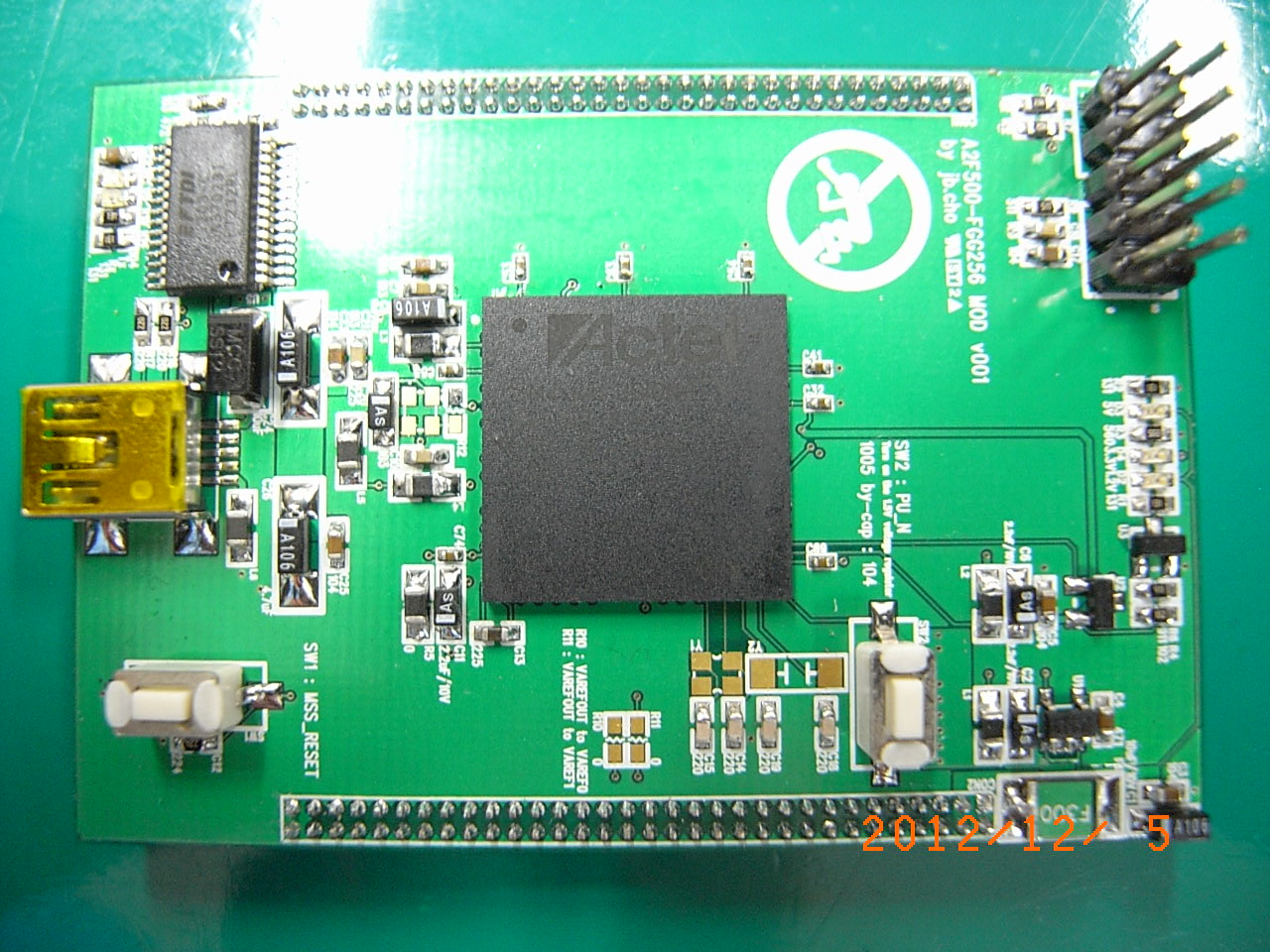

예전에 만들었던 EP4CE22E22 모듈을 쓸 예정이니까 FPGA 스펙부터 확인하자.

- Logic elements(LEs) : 22,320

- Embedded memory(Kbits) : 594

- Embedded 18 x 18 multipliers : 66

- General-purpose PLLs : 4

- Global Clock Networks : 20

- User I/O Banks : 8

- Maximum user I/O : 153

하드웨어 구성은

- Nios II/s processor core

- On-chip memory

- UART

요 세가지로 하자.

1. SW version

- Quartus II 64-Bit version 12.0 Build 178 05/31/2012 SJ Full Version

- NIOS II EDS 12.0

*. NIOS II를 오픈코어 플러스 평가판 라이센스로 돌려도 된다. 제한이 무지 많으니까 명심하도록.

2. Quartus II 프로젝트 생성

- NIOSII_Start 폴더를 만들고 프로젝트 이름도 똑같이 만들었다. Next

- 추가할 파일 없으니까 그냥 Next

- EP4CE22E22C8N 이니까 해당하는 디바이스 선택 후 Next

- 여긴 걍 통과. Next

- 다 만들었다. Finish

- 자 준비는 끝났고, 시작해 봅시다.

3. Block Diagram File 생성

- Quartus II 의 File -> New

- Block Diagram/Schematic File 선택 후 OK

- Save Project 해주자.

4. Create a New Qsys System

- Quartus의 Tool메뉴에서 Qsys를 클릭해라. 아래 창이 뜰거다

- 일단 Nios II 프로세서부터 붙여보자.

- 저걸 더블클릭해라.

- Nios II 코어는 3종류다. 난 일단 Nios II/f을 선택했다. 다른설정 건드릴거 없이 Finish

- On-Chip 메모리 붙일 차례. 저거 더블클릭.

- Total memory size만 32768로 변경하고 Finish.

디바이스의 메모리 용량이 크면 이거보다 크게해도 상관없다.

EP4CE22E22의 메모리 절반 정도의 사이즈다.

- 마지막으로 UART 붙일 차례. 저거 더블클릭

- 보레잇 115200으로 Fixed baud rate 설정해준다. Finish

- 여기까지 사용할 컴포넌트는 다 추가했다.

- 다음은 모듈간 연결을 해줄 차례다. 위 그림과 같이 연결하면 된다.

외부로 빠질 시그널은 CLK, RST, UART Rx/Tx 다. Export 창을 클릭하면 된다.

- System의 Assign Base Addresses를 클릭해봐라.

Base 컬럼의 16진수값이 변경될거다.

- System의 Assign Interrupt Numbers를 클릭해봐라.

IRQ 컬럼의 값이 생성된다.

- Nios2_qsys_0를 더블클릭해서 윗 그림처럼 변경해라.

- Generation 탭에서 Generate를 클릭하면 그토록 염원하던 니오스 코어가 생성된다.

중간중간 워닝이 뜨지만 일단 무시하자.

5. Quartus II에 Nios II 붙이기

- Quartus II의 bdf 창을 더블클릭 해보시라.

- 이런 창이 뜬다.

- Libraries에 Project를 열어보면 방금 만든 Nios 코어가 보인다. OK

- 여기에 클럭, 리셋, UART Rx/Tx만 연결하면 된다.

- 이렇게 연결하고 Save Project. 다음은 qip 파일을 추가한다.

- Asignments의 Setting로 가자.

Nios 코어 폴더내의 synthesis 폴더내에 NIOSIIf_UART.qip 파일이 있다.

add 하고 OK.

- DEV_CLRn에 스위치를 연결해서 써먹을란다. 저거 Enable.

- 핀 할당 해줘야 하니까 Analysis & Synthesis 실행하자.

- 회로 설계한대로 핀 할당 해준다. 그 다음은 Start Compilation.

담배한대 피고...

일단 여기까지 Hardware는 만들었다.

다음은 NIOS II EDS로 간단한 디버깅 프로그램을 만들어보자.